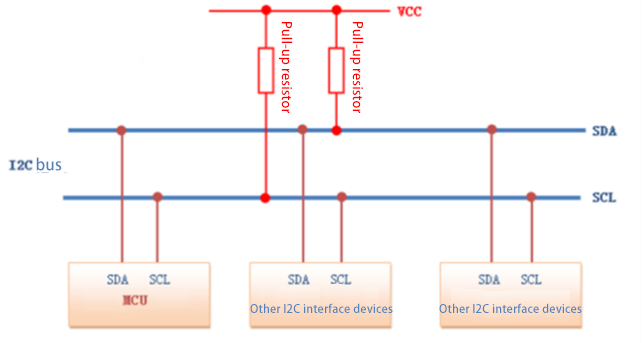

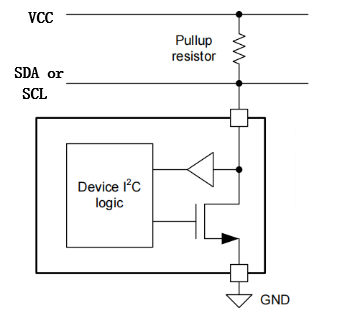

在设计 IIC 接口的外围电路时,我们通常使用图 1 所示的带上拉电阻的拓扑图,其内部结构为图 2 所示的开漏输出。

开漏输出电平由外部上拉电阻和内部逻辑电路控制,从而实现总线的低电平拉低和释放。总线开漏电路包含一个NMOS晶体管,该晶体管由控制信号控制其导通和关断。当控制信号导通NMOS晶体管时,输出为低电平。当控制信号关断NMOS晶体管时,输出处于浮空状态,需要外部上拉电阻才能输出高电平。

这种结构使得开漏栅极能够灵活地控制总线电平,同时避免直接驱动总线,从而确保多个设备之间的安全连接和通信。使用这种开漏输出的优势显而易见,体现在以下几个方面:

1. 短路预防

如果采用推挽式配置而非开漏式配置,且多个器件连接到同一总线上,当一个器件的 I/O 输出高电平而另一个器件的 I/O 输出低电平时,这两个 I/O 的 VCC 和 GND 连接将发生短路,导致电路损坏。然而,开漏式配置可以避免这个问题。无论总线上连接多少器件,都不会出现电源短路的风险。

2. 提高驱动能力并降低功耗

在漏极输出引脚上连接一个上拉电阻可以实现电平转换,并提供更强的驱动能力。这利用了外部电路的驱动能力来降低IC内部的驱动电流。当IC内部的MOSFET导通时,驱动电流从外部VCC流经上拉电阻Rpull-up、MOSFET,然后流向GND。IC内部只需要很小的栅极驱动电流。

3. 使用“有线与”运算来确定总线活动状态

多个开漏输出引脚可以连接到同一条线上,形成“与”逻辑关系,称为“线与”功能。当其中一个引脚为低电平时,开漏线上的逻辑电平变为0。I2C总线也使用这一原理来判断总线是否处于活动状态。

4. 促进产量水平的转变

可以通过改变上拉电源电压来改变传输电平,而输出高电平由 VDD 决定。